Motorola MVME2600 series Installation And Use Manual

Single board computer

Hide thumbs

Also See for MVME2600 series:

- Reference manual (283 pages) ,

- Installation and use manual (20 pages) ,

- Programmer's reference manual (20 pages)

Table of Contents

Advertisement

Quick Links

Download this manual

See also:

Reference Manual

Advertisement

Chapters

Table of Contents

Summary of Contents for Motorola MVME2600 series

- Page 1 MVME2600 Series Single Board Computer Installation and Use V2600A/IH3 July 2001 Edition...

- Page 2 © Copyright 1998, 2001 Motorola, Inc. All rights reserved. Printed in the United States of America. ® Motorola and the Motorola symbol are registered trademarks of Motorola, Inc. ® is a registered trademark of International Business Machines Corporation. ® PowerPC is a registered trademark of International Business Machines.

-

Page 3: Safety Summary

The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment. -

Page 4: Emi Caution

Flammability All Motorola PWBs (printed wiring boards) are manufactured with a flammability rating of 94V-0 by UL-recognized manufacturers. EMI Caution This equipment generates, uses and can radiate electromagnetic energy. It may cause or be susceptible to electromagnetic interference (EMI) if not installed and used with adequate EMI protection. - Page 5 While reasonable efforts have been made to assure the accuracy of this document, Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

- Page 6 If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply unless otherwise agreed to in writing by Motorola, Inc. Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in Technical Data clause at DFARS 252.227-7013 (Nov.

-

Page 7: Table Of Contents

Contents About This Manual Summary of Changes ....................xviii Overview of Contents ....................xviii Comments and Suggestions ..................xix Conventions Used in This Manual................xx CHAPTER 1 Hardware Preparation and Installation Introduction........................1-1 Equipment Required ....................1-3 Overview of Startup Procedure..................1-3 Unpacking Instructions ....................1-5 Hardware Configuration ....................1-5 MVME2603/2604 Base Board Preparation ...............1-6 Cache Mode Control (J3)..................1-7 Flash Bank Selection (J10) .................1-7... - Page 8 MVME712M Transition Module Installation ..........1-44 MVME761 Transition Module Installation............1-48 System Considerations .................... 1-50 MVME2603/2604 VME Module ..............1-51 CHAPTER 2 Operating Instructions Introduction ....................... 2-1 Applying Power ......................2-1 ABORT Switch (S1)................... 2-3 RESET Switch (S2).................... 2-3 Front Panel Indicators (DS1 – DS6)..............2-4 Memory Maps......................

- Page 9 Disk Drive Controller ................3-10 Keyboard and Mouse Interface..............3-10 PCI-ISA Bridge (PIB) Controller ..............3-10 Real-Time Clock/NVRAM/Timer Function .............3-11 Programmable Timers..................3-12 Interval Timers ..................3-12 16-Bit Timers.....................3-13 Serial Communications Interface..............3-13 Z8536 CIO Device..................3-14 Base Module Feature Register ................3-14 P2 Signal Multiplexing ..................3-15 ABORT Switch (S1) ..................3-16 RESET Switch (S2) ..................3-16 Front Panel Indicators (DS1 –...

- Page 10 Ethernet AUI Connector................... 4-24 MVME761-Compatible Versions ................4-25 VMEbus Connector P2..................4-25 Serial Ports 1 and 2................... 4-26 Serial Ports 3 and 4................... 4-27 Parallel Connector .................... 4-28 Ethernet 10BaseT/100BaseTX Connector ............4-29 CHAPTER 5 PPCBug Overview ........................5-1 Memory Requirements ..................5-2 PPCBug Implementation ..................

- Page 11 APPENDIX C Troubleshooting CPU Boards: Solving Startup Problems Introduction....................... C-1 APPENDIX D Related Documentation Motorola Computer Group Documents ..............D-1 Manufacturers’ Documents..................D-2 Related Specifications....................D-5...

- Page 13 List of Figures Figure 1-1. MVME2603/2604 Base Board Block Diagram ........1-2 Figure 1-2. MVME2603/2604 Switches, Headers, Connectors, Fuses, LEDs ..1-9 Figure 1-3. MVME712M Connector and Header Locations ........1-16 Figure 1-4. J15 Clock Line Configuration ...............1-17 Figure 1-5. MVME712M Serial Port 1 DCE/DTE Configuration ......1-18 Figure 1-6.

- Page 15 List of Tables Table 1-1. Startup Overview ..................1-3 Table 1-2. MVME712M Port/Jumper Correspondence...........1-17 Table 2-1. Processor Default View of the Memory Map ...........2-6 Table 2-2. PCI Arbitration Assignments..............2-10 Table 2-3. IBC DMA Channel Assignments ............2-13 Table 2-4. Classes of Reset and Effectiveness ............2-14 Table 3-1.

- Page 16 Table B-2. EIA-232-D Interface Transmitter Characteristics ......... B-5 Table B-3. EIA-232-D Interface Receiver Characteristics ........B-5 Table B-4. MVME761 EIA-530 Interconnect Signals ..........B-6 Table B-5. EIA-530 Interface Transmitter Characteristics ........B-8 Table B-6. EIA-530 Interface Receiver Characteristics .......... B-9 Table C-1.

-

Page 17: About This Manual

About This Manual This manual provides general information, hardware preparation and installation instructions, operating instructions, and a functional description of the MVME2603/2604 family of single board computers. As of the publication date, the information presented in this manual applies to the following MVME2603 and MVME2604 models: Model Number Description MVME2603-1121C to... -

Page 18: Summary Of Changes

Summary of Changes This is the third edition of the Installation and Use manual. It supersedes the May 1998 edition and incorporates the following updates. Date Changes Replaces July 2001 All data referring to the VME CSR Bit Set Register V2600A/IH2 (VCSR_SET) and VME CSR Bit Clear Register (VCSR_CLR) has been deleted. -

Page 19: Comments And Suggestions

Documentation, lists all documentation related to the MVME2603/2604 single board computer. Comments and Suggestions Motorola welcomes and appreciates your comments on its documentation. We want to know what you think about our manuals and how we can make them better. Mail comments to:... -

Page 20: Conventions Used In This Manual

Conventions Used in This Manual The following typographical conventions are used in this document: bold is used for user input that you type just as it appears; it is also used for commands, options and arguments to commands, and names of programs, directories and files. -

Page 21: Introduction

1Hardware Preparation and Installation Introduction The MVME2603/2604 is a single-slot VME module equipped with a ® PowerPC Series microprocessor. The MVME2603 is equipped with a ™ ™ PowerPC 603 microprocessor; the MVME2604 has a PowerPC 604 microprocessor. 256KB L2 cache (level 2 secondary cache memory) is available as an option on all versions. -

Page 22: Figure 1-1. Mvme2603/2604 Base Board Block Diagram

Hardware Preparation and Installation CLOCK DEBUG CONNECTOR MEMORY EXPANSION CONNECTORS GENERATOR L2 CACHE 256K FLASH FLASH 4MB or 8MB PROCESSOR SYSTEM MPC603/604 REGISTERS PHB & MPIC MEMORY CONTROLLER RAVEN ASIC FALCON CHIPSET 33MHz 32/64-BIT PCI LOCAL BUS ETHERNET SCSI VME BRIDGE W83C553 DEC21140 53C825A... -

Page 23: Equipment Required

MVME761 Transition Module Preparation on page 1-25 Ensure memory mezzanines are RAM200 Memory Mezzanine Installation on page 1-35 properly installed on the base board. Install the MVME2603/2604 VME MVME2603/2604 VME Module Installation on page module in the chassis. 1-42 http://www.motorola.com/computer/literature... - Page 24 5-3, Debugger Commands, the SET command Examine and/or change Chapter 6, CNFG and ENV Commands environmental parameters. Program the board as needed for MVME2600 Series Single Board Computer your applications. Programmer’s Reference Guide, listed in Appendix D, Related Documentation. Computer Group Literature Center Web Site...

-

Page 25: Unpacking Instructions

Series Single Board Computer Programmer’s Reference Guide, as listed in Appendix D, Related Documentation.) Some options, however, are not software-programmable. Such options are controlled through manual installation or removal of header jumpers or interface modules on the base board or the associated transition module. http://www.motorola.com/computer/literature... -

Page 26: Mvme2603/2604 Base Board Preparation

Hardware Preparation and Installation MVME2603/2604 Base Board Preparation Figure 1-2 on page 1-9 illustrates the placement of the switches, jumper headers, connectors, and LED indicators on the MVME2603/2604. Manually configurable items on the base board include: Cache mode control (J3) Flash bank selection (J10) Serial Port 4 receive clock configuration (J16) Serial Port 4 transmit clock configuration (J17) -

Page 27: Cache Mode Control (J3)

1 and 2. To enable Flash bank B (1MB of firmware located in sockets on the base board), place a jumper across header J10 pins 2 and 3. Flash Bank A Enabled (4MB/8MB, Soldered) Flash Bank B Enabled (1MB, Sockets) (factory configuration) http://www.motorola.com/computer/literature... -

Page 28: Serial Port 4 Receive Clock Configuration (J16)

Hardware Preparation and Installation Serial Port 4 Receive Clock Configuration (J16) In synchronous serial communications, you can configure Serial Port 4 on the MVME2603/2604 to use the clock signals provided by the RxC signal line. On MVME712M-compatible versions of the base board, header J16 configures port 4 to either drive or receive RxC. -

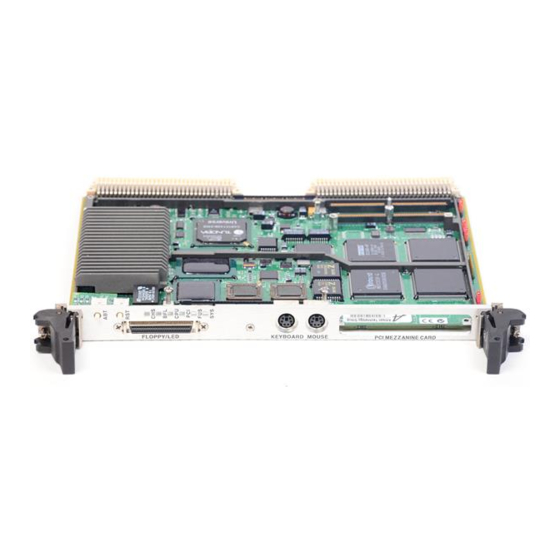

Page 29: Figure 1-2. Mvme2603/2604 Switches, Headers, Connectors, Fuses, Leds

MVME2603/2604 Base Board Preparation Figure 1-2. MVME2603/2604 Switches, Headers, Connectors, Fuses, LEDs http://www.motorola.com/computer/literature... -

Page 30: Serial Port 4 Transmit Clock Configuration (J17)

Hardware Preparation and Installation Serial Port 4 Transmit Clock Configuration (J17) In synchronous serial communications, you can configure Serial Port 4 on the MVME2603/2604 to use the clock signals provided by the TxC signal line. Header J17 configures port 4 to either drive or receive TxC. The factory configuration has port 4 set to receive TxC. -

Page 31: Serial Port 4 Transmit Clock Receiver Buffer Control (J20)

Figure 1-9 Figure 1-10 (for the MVME712M) and Figure 1-14 Figure 1-15 (for the MVME761) diagram the overall jumper settings required on the MVME2603/2604 and transition module for a Serial Port 4 DCE or DTE configuration. http://www.motorola.com/computer/literature 1-11... -

Page 32: Serial Port 3 Transmit Clock Configuration (J18)

Hardware Preparation and Installation For additional details on the configuration of those headers, refer to MVME712M Transition Module Preparation on page 1-14, MVME761 Transition Module Preparation on page 1-25, or to the respective user’s manuals for the transition modules (listed in Appendix D, Related Documentation) as necessary. -

Page 33: System Controller Selection (J22)

J22 pins 1 and 2. When the board is functioning as system controller, the SCON LED is turned on. Not System Controller Auto System Controller System Controller (factory configuration) http://www.motorola.com/computer/literature 1-13... -

Page 34: Remote Status And Control

Hardware Preparation and Installation Remote Status and Control The MVME2603/2604 front panel LEDs and switches are mounted on a removable mezzanine board. Removing the LED mezzanine makes the mezzanine connector (J1, a keyed double-row 14-pin connector) available for service as a remote status and control connector. In this application, J1 can be connected to a user-supplied external cable to carry the Reset and Abort signals and the LED lines to a control panel located apart from the MVME2603/2604. - Page 35 MVME712M Transition Module Preparation Socket-mounted SCSI terminating resistors for end-of-cable or middle-of-cable configurations Fused SCSI terminator power developed from the +5VDC present at connector P2 A 64-pin DIN connector to interface the EIA-232-D, parallel, SCSI, and Ethernet signals to the MVME712M http://www.motorola.com/computer/literature 1-15...

-

Page 36: Figure 1-3. Mvme712M Connector And Header Locations

Hardware Preparation and Installation MVME712M Figure 1-3. MVME712M Connector and Header Locations 1-16 Computer Group Literature Center Web Site... -

Page 37: Serial Ports 1-4 Dce/Dte Configuration

TRXC4 TO PORT 4 PIN 15 RTXC4 TO PORT 4 PIN 24 TRXC4 TO PORT 4 PIN 17 RTXC4 TO PORT 4 PIN 17 TRXC4 TO PORT 4 PIN 24 RTXC4 TO PORT 4 PIN 15 Figure 1-4. J15 Clock Line Configuration http://www.motorola.com/computer/literature 1-17... -

Page 38: Figure 1-5. Mvme712M Serial Port 1 Dce/Dte Configuration

Hardware Preparation and Installation MVME2603/2604 P2 ADAPTER 64-PIN MVME712M BOARD CABLE MODULE PC87308 SOUT1 RTS1# DTR1# +12V SIN1 CTS1# DCD1# +12V DSR1# R11# 11551.00 9609 (1-8) MVME2603/2604 P2 ADAPTER 64-PIN MVME712M BOARD CABLE MODULE PC87308 SOUT1 RTS1# DTR1# +12V SIN1 CTS1# DCD1# DSR1#... -

Page 39: Figure 1-6. Mvme712M Serial Port 2 Dce/Dte Configuration

DTR2# SIN2 CTS2# DCD2# DSR2# +12V R12# 11551.00 9609 (3-8) MVME2603/2604 P2 ADAPTER 64-PIN MVME712M BOARD CABLE MODULE PC87308 SOUT2 RTS2# DTR2# SIN2 CTS2# DCD2# DSR2# R12# 11551.00 9609 (4-8) Figure 1-6. MVME712M Serial Port 2 DCE/DTE Configuration http://www.motorola.com/computer/literature 1-19... -

Page 40: Figure 1-7. Mvme712M Serial Port 3 Dce Configuration

Hardware Preparation and Installation MVME2603/2604 64-PIN MVME712M ADAPTER CABLE MODULE Z85230 TXDA RTSA# DCDA# RXDA CTSA# TRXCA# RTXCA# Z8536 DTR3# LLB3# RLB3# DSR3# +12V R13# TM3# NOTE: J18 OPEN 11551.00 9609 (5-8) Figure 1-7. MVME712M Serial Port 3 DCE Configuration 1-20 Computer Group Literature Center Web Site... -

Page 41: Figure 1-8. Mvme712M Serial Port 3 Dte Configuration

MVME712M Transition Module Preparation MVME2603/2604 64-PIN MVME712M ADAPTER CABLE MODULE DB25 Z85230 TXDA RTSA# DCDA# RXDA CTSA# TRXCA# RTXCA# Z8536 DTR3# LLB3# RLB3# DSR3# R13# TM3# NOTE: J18 OPEN 11551.00 9609 (6-8) Figure 1-8. MVME712M Serial Port 3 DTE Configuration http://www.motorola.com/computer/literature 1-21... -

Page 42: Figure 1-9. Mvme712M Serial Port 4 Dce Configuration

Hardware Preparation and Installation MVME2603/2604 64-PIN MVME712M ADAPTER CABLE MODULE DB25 Z85230 TXDB RTSB# DCDB# RXDB CTSB# TXCI RXCI TXCO TRXCB RTXCB Z8536 DTR4# LLB4# RLB4# DSR4# +12V R14# TM4# NOTE: J20 OPEN J16 1-2 J17 1-2 11551.00 9609 (7-8) Figure 1-9. -

Page 43: Figure 1-10. Mvme712M Serial Port 4 Dte Configuration

MODULE DB25 Z85230 TXDB RTSB# DCDB# RXDB CTSB# TXCI RXCI TXCO TRXCB RTXCB Z8536 DTR4# LLB4# RLB4# DSR4# R14# TM4# NOTE: J20 1-2 J16 2-3 J17 2-3 11551.00 9609 (8-8) Figure 1-10. MVME712M Serial Port 4 DTE Configuration http://www.motorola.com/computer/literature 1-23... -

Page 44: P2 Adapter Preparation

Hardware Preparation and Installation P2 Adapter Preparation Preparation of the P2 adapter for the MVME712M consists of removing or installing the SCSI terminating resistors. Figure 1-11 illustrates the location of the resistors, fuse, and connectors. For further information on the preparation of the transition module and the P2 adapter, refer to the user’s manual for the MVME712M (listed in Appendix D, Related Documentation) as necessary. -

Page 45: Mvme761 Transition Module Preparation

The features of the P2 adapter board for the MVME761 include: A 50-pin connector for SCSI cabling to SCSI devices Jumper-selectable SCSI terminating resistors Fused SCSI terminator power developed from the +5V DC present at connector P2 A 64-pin 3M connector to the MVME761 http://www.motorola.com/computer/literature 1-25... -

Page 46: Figure 1-12. Mvme761 Connector And Header Locations

Hardware Preparation and Installation MVME 761-001 Figure 1-12. MVME761 Connector and Header Locations 1-26 Computer Group Literature Center Web Site... -

Page 47: Serial Ports 1 And 2

X.21 (DCE and DTE) You can configure Serial Ports 3 and 4 for any of the above serial protocols by installing the appropriate serial interface module and setting the corresponding jumper. SIMs can be ordered separately as required. http://www.motorola.com/computer/literature 1-27... - Page 48 Hardware Preparation and Installation Headers J2 and J3 are used to configure Serial Port 3 and Serial Port 4, respectively, in tandem with SIM selection. With the jumper in position 1-2, the port is configured as a DTE. With the jumper in position 2-3, the port is configured as a DCE.

-

Page 49: Figure 1-13. Mvme761 Serial Ports 1 And 2 (Dce Only)

MVME761 Transition Module Preparation MVME2603/2604 MVME761 SOUT1 RTS1# DTR1# SIN1 COM1 CTS1# DSR1# DCD1# RI1# PC87308 P2/P2MX SOUT2 RTS2# DTR2# SIN2 CTS2# COM2 DSR2# DCD2# RI2# 11552.00 9609 (1-3) Figure 1-13. MVME761 Serial Ports 1 and 2 (DCE Only) http://www.motorola.com/computer/literature 1-29... -

Page 50: Figure 1-14. Mvme761 Serial Ports 3 And 4 Dce Configuration

Hardware Preparation and Installation MVME761 MVME3600 SERIES Z85230 SCC HD26 EIA232-DCE SIM RTS# CTS# DCD# J2/J3 TRXC RTXC P2/P2MX Z8536 CIO DTR# LLB# RLB# DSR# 11552.00 9802 (2-5) Figure 1-14. MVME761 Serial Ports 3 and 4 DCE Configuration 1-30 Computer Group Literature Center Web Site... -

Page 51: Figure 1-15. Mvme761 Serial Ports 3 And 4 Dte Configuration

MVME761 Transition Module Preparation MVME3600 SERIES MVME761 Z85230 SCC HD26 EIA232-DTE SIM RTS# CTS# DCD# J2/J3 TRXC RTXC P2/P2MX Z8536 CIO DTR# LLB# RLB# DSR# 11552.00 9802 (4-5) Figure 1-15. MVME761 Serial Ports 3 and 4 DTE Configuration http://www.motorola.com/computer/literature 1-31... -

Page 52: P2 Adapter Preparation (Three-Row)

Hardware Preparation and Installation P2 Adapter Preparation (Three-Row) The P2 adapter for the MVME761 transition module routes the synchronous and asynchronous serial, parallel, and Ethernet signals to the MVME761. The P2 adapter also has a 50-pin female connector (J2) that carries 8-bit SCSI signals from the MVME2603/2604. -

Page 53: P2 Adapter Preparation (Five-Row)

The MVME761 transition module uses a five-row P2 adapter to transfer the synchronous and asynchronous serial, parallel, and Ethernet signals to and from the MVME2600 series VME module. The P2 adapter has a 68-pin female connector (J1) that carries 16-bit SCSI signals from the MVME2600. -

Page 54: Figure 1-17. Mvme761 P2 Adapter (Five-Row) Component Placement

Hardware Preparation and Installation For further information on the preparation of the transition module and the P2 adapter, refer to the user’s manual for the MVME761 (listed in Appendix D, Related Documentation) as necessary. 1999 9701 Figure 1-17. MVME761 P2 Adapter (Five-Row) Component Placement 1-34 Computer Group Literature Center Web Site... -

Page 55: Hardware Installation

Should it be necessary to install mezzanines on the base board, refer to the following sections for a brief description of the installation procedure. Motorola strongly recommends that you use an antistatic wrist strap and a Use ESD conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to electrostatic discharge (ESD). - Page 56 Hardware Preparation and Installation 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure. 2.

-

Page 57: Pmc Module Installation

AC or DC power source, and turn the equipment power on. PMC Module Installation PCI mezzanine card (PMC) modules mount beside the RAM200 mezzanine on top of the MVME2603/2604 base board. To install a PMC module, refer to Figure 1-19 and proceed as follows: http://www.motorola.com/computer/literature 1-37... - Page 58 Hardware Preparation and Installation 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. The ESD strap must be secured to your wrist and to ground throughout the procedure. 2.

-

Page 59: Figure 1-19. Pmc Module Placement On Mvme2603/2604

Do not damage or bend connector pins. 8. Replace the chassis or system cover(s), reconnect the system to the AC or DC power source, and turn the equipment power on. http://www.motorola.com/computer/literature 1-39... -

Page 60: Pmc Carrier Board Installation

Hardware Preparation and Installation PMC Carrier Board Installation PCI mezzanine card (PMC) carrier boards mount above the RAM200 mezzanine and (if installed) PMC module on the MVME2603/2604 base board. To install a PMC carrier board for additional PCI expansion, refer Figure 1-20 and proceed as follows: 1. -

Page 61: Figure 1-20. Pmc Carrier Board Placement On Mvme2603/2604

Hardware Installation 11661.00 9611 (1-3) Figure 1-20. PMC Carrier Board Placement on MVME2603/2604 5. Remove the LED module screw located at the upper front corner of the base board. Install a short (0.394 inch) standoff in its place. http://www.motorola.com/computer/literature 1-41... -

Page 62: Mvme2603/2604 Vme Module Installation

Hardware Preparation and Installation 6. At the other three corners of the base board, install long (0.737 inch) standoffs. 7. Place the PMC carrier board on top of the base board. The connector on the underside of the carrier board should connect smoothly with the corresponding connector J5 (located between P1 and P2) on the MVME2603/2604. - Page 63 (BG) jumpers from the header for the card BUS GRANT slot occupied by the MVME2603/2604. Note Some VME backplanes (for example, those used in Motorola "Modular Chassis" systems) have an auto-jumpering feature for automatic propagation of the IACK and BG signals. Step does not apply to such backplane designs.

-

Page 64: Mvme712M Transition Module Installation

Hardware Preparation and Installation 7. If necessary, install an MVME712M or MVME761 transition module and cable it to the MVME2603/2604 as described in the following sections of this document. 8. Replace the chassis or system cover(s), cable peripherals to the panel connectors as appropriate, reconnect the system to the AC or DC power source, and turn the equipment power on. - Page 65 Figure 1-21 shows a possible configuration for use with internal SCSI devices. For more detailed information on installing the P2 adapter board and the MVME712M transition module, refer to the user’s manual (listed in Appendix D, Related Documentation). http://www.motorola.com/computer/literature 1-45...

- Page 66 Note Not all peripheral cables are provided with the MVME712M; you may need to fabricate or purchase certain cables. (To minimize radiation, Motorola recommends shielded cable for peripheral connections where possible.) 1-46 Computer Group Literature Center Web Site...

-

Page 67: Figure 1-21. Mvme712M/Mvme2603/2604 Cable Connections

Hardware Installation TERMINATORS SCSI INSTALLED DEVICE SCSI DEVICE MVME712M MVME2600 50-CONDUCTOR CABLE 64-CONDUCTOR CABLE P2 ADAPTER TERMINATORS TERMINATORS REMOVED INSTALLED ENCLOSURE BOUNDARY cb2349301 Figure 1-21. MVME712M/MVME2603/2604 Cable Connections http://www.motorola.com/computer/literature 1-47... -

Page 68: Mvme761 Transition Module Installation

Hardware Preparation and Installation MVME761 Transition Module Installation This section applies to MVME761-compatible models of the MVME2603/2604 VME module. With the MVME2603/2604 installed, refer to Figure 1-22 and proceed as follows to install an MVME761 transition module: 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. -

Page 69: Figure 1-22. Mvme761/Mvme2603/2604 Cable Connections

5. Route the 64-conductor cable furnished with the MVME761 from J3 on the P2 adapter board to P2 on the transition module. Be sure to orient cable pin 1 with connector pin 1. Avoid touching areas of integrated circuitry; static discharge can damage these circuits Caution http://www.motorola.com/computer/literature 1-49... -

Page 70: System Considerations

Note Not all peripheral cables are provided with the MVME761; you may need to fabricate or purchase certain cables. (To minimize radiation, Motorola recommends shielded cable for peripheral connections where possible.) System Considerations The MVME2603/2604 draws power from VMEbus backplane connectors P1 and P2. -

Page 71: Mvme2603/2604 Vme Module

VMEbus devices see this local DRAM at base physical address $00000000, as programmed by the firmware. This may be changed via software to any other base address. Refer to the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation, for more information. - Page 72 Hardware Preparation and Installation the 14-pin combined LED-mezzanine/remote-reset connector, J1. The LED (DS5) on the MVME2603/2604 front panel illuminates when all three voltages are available. In MVME712M I/O mode, the MVME2603/2604 supplies SCSI terminator power through a 1A fuse (F1) located on the P2 adapter board. If the fuse is blown, the SCSI device(s) may function erratically or not at all.

- Page 73 After power-up you can reconfigure the baud rate if you wish, using the PPCBug PF (Port Format) command via the command line interface. Whatever the baud rate, some type of hardware handshaking — either XON/OFF or via the RTS/CTS line — is desirable if the system supports it. http://www.motorola.com/computer/literature 1-53...

-

Page 75: Introduction

2Operating Instructions Introduction This chapter supplies information for use of the MVME2603/2604 family of Single Board Computers in a system configuration. Here you will find the power-up procedure and descriptions of the switches and LEDs, memory maps, and software initialization. Applying Power After you have verified that all necessary hardware preparation has been done, that all connections have been made correctly, and that the... -

Page 76: Figure 2-1. Ppcbug System Startup

Operating Instructions STARTUP SYSTEM INITIALIZATION CONSOLE DETECTION RUN SELFTESTS (IF ENABLED) AUTOBOOT (IF ENABLED) OPERATING SYSTEM 11734.00 9702 Figure 2-1. PPCBug System Startup The MVME2603/2604 front panel has switches and six ABORT RESET LED (light-emitting diode) status indicators ( ). The switches and LEDs are mounted on an LED mezzanine board that plugs into the base board. -

Page 77: Abort Switch (S1)

The local reset driver is enabled even when the Universe ASIC is not system controller. Local resets may be generated by the switch, a power-up reset, a watchdog timeout, a VMEbus RESET ∗ , or a control bit in the MISC_CTL register. SYSRESET http://www.motorola.com/computer/literature... -

Page 78: Front Panel Indicators (Ds1 - Ds6)

Operating Instructions Front Panel Indicators (DS1 – DS6) There are six LEDs on the MVME2603/2604 front panel: , and (DS1, yellow). Checkstop; driven by the MPC603/604 status lines on the MVME2603/2604. Lights when a halt condition from the processor is detected. ∗... -

Page 79: Memory Maps

The following sections give a general description of the MVME2603/2604 memory organization from the above three points of view. Detailed memory maps can be found in the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation. -

Page 80: Default Processor Memory Map

Operating Instructions Default Processor Memory Map The default processor memory map that is valid at power-up or reset remains in effect until reprogrammed for specific applications. Table 2-1 defines the entire default map ($00000000 to $FFFFFFFF). Table 2-2 further defines the map for the local I/O devices (accessible through the PCI/ISA I/O Space). -

Page 81: Pci Local Bus Memory Map

For detailed PCI memory maps, including suggested CHRP- and PREP- compatible memory maps, refer to the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation. -

Page 82: Programming Considerations

Operating Instructions Programming Considerations Good programming practice dictates that only one MPU at a time have control of the MVME2603/2604 control registers. Of particular note are: Registers that modify the address map Registers that require two cycles to access VMEbus interrupt request registers Computer Group Literature Center Web Site... -

Page 83: Figure 2-2. Vmebus Master Mapping

RESOURCES NOTES: 1. Programmable mapping done by Raven ASIC. 11553.00 9609 2. Programmable mapping performed via PCI Slave images in Universe ASIC. 3. Programmable mapping performed via Special Slave image (SLSI) in Universe ASIC. Figure 2-2. VMEbus Master Mapping http://www.motorola.com/computer/literature... -

Page 84: Pci Arbitration

The PIB supports flexible arbitration modes of fixed priority, rotating priority, and mixed priority, as appropriate in a given application. Details on PCI arbitration can be found in the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation. -

Page 85: Interrupt Handling

The PCI bus (interrupts from PCI devices) The ISA bus (interrupts from ISA devices) Figure 2-3 illustrates interrupt architecture on the MVME2603/2604. For details on interrupt handling, refer to the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation. -

Page 86: Figure 2-3. Mvme2603/Mvme2604 Interrupt Architecture

Operating Instructions INT_ Processor (8529 Pair) MCP_ RavenMPIC SERR_& PERR_ PCI Interrupts ISA Interrupts 11559.00 9609 Figure 2-3. MVME2603/MVME2604 Interrupt Architecture 2-12 Computer Group Literature Center Web Site... -

Page 87: Dma Channels

The MVME2603/2604 SBC has eight potential sources of reset: 1. Power-on reset switch (resets the VMEbus when the MVME2603/2604 is RESET system controller) 3. Watchdog timer Reset function controlled by the SGS-Thomson MK48T559 timekeeper device (resets the VMEbus when the MVME2603/2604 is system controller) http://www.motorola.com/computer/literature 2-13... -

Page 88: Table 2-4. Classes Of Reset And Effectiveness

System Software reset and Local Software Reset. The following table shows which devices are affected by the various types of resets. For details on using resets, refer to the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation. -

Page 89: Endian Issues

The following sections summarize how the MVME2603/2604 handles software and hardware differences in big- and little-endian operations. For further details on endian considerations, refer to the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation. -

Page 90: Vmebus Domain

Operating Instructions PCI and SCSI SCSI is byte-stream-oriented; the byte having the lowest address in memory is the first one to be transferred regardless of the endian mode. Since the Raven ASIC maintains address invariance in both little-endian and big-endian modes, no endian issues should arise for SCSI data. Big-endian software must still take the byte-swapping effect into account when accessing the registers of the PCI/SCSI device, however. -

Page 91: Introduction

3Functional Description Introduction This chapter describes the MVME2603/2604 single board computer on a block diagram level. The General Description provides an overview of the MVME2603/2604, followed by a detailed description of several blocks of circuitry. Figure 3-1 shows a block diagram of the overall board architecture. - Page 92 Functional Description Table 3-1. MVME2603/2604 Features (Continued) Feature Description Tick timers Four programmable 16-bit timers (one in S82378ZB ISA bridge; three in Z8536 CIO device) Watchdog timer Provided in SGS-Thomson M48T59 Interrupts Software interrupt handling via Raven (PCI-MPU bridge) and Winbond (PCI-ISA bridge) controllers VME I/O VMEbus P2 connector...

-

Page 93: General Description

I/O expansion through FDDI (Fiber Distributed Data Interface), ATM (Asynchronous Transfer Mode), graphics, Ethernet, or SCSI ports. The base board supports PMC front panel I/O. There is also provision for additional expansion via a PMC carrier board. http://www.motorola.com/computer/literature... -

Page 94: Block Diagram

Functional Description Block Diagram Figure 3-1 is a block diagram of the MVME2603/2604’s overall architecture. PS/2 Floppy Processor L2 Cache Parallel Keyboard Mouse Async Serial 60X System Bus ISA SIO Sync Serial Falcon Dram Falcon ISA Local Resource Bus FLASH NVRAM Raven ISA CSR... -

Page 95: Scsi Interface

In MVME761 I/O mode, the P2 adapter board used with the MVME761 has a jumper to enable/disable SCSI bus terminators. +5V DC power for SCSI termination is supplied through a polyswitch located on the adapter board. http://www.motorola.com/computer/literature... -

Page 96: Ethernet Interface

Functional Description Ethernet Interface The MVME2603/2604 VME module uses Digital Equipment’s DECchip 21140 PCI Fast Ethernet LAN controller to implement an Ethernet interface that supports both AUI (via MVME712M) and 10BaseT/100BaseTX (via MVME761) connections. The balanced differential transceiver lines are coupled via on-board transformers. The MVME2603/2604 routes its AUI and 10BaseT/100BaseTX lines through the P2 connector to the transition module (as illustrated in Figure... -

Page 97: Pci Mezzanine Interface

Block Diagram map description in the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation, for detailed programming information. PCI Mezzanine Interface A key feature of the MVME2603/2604 family is the PCI (Peripheral Component Interconnect) bus. In addition to the on-board local bus devices (SCSI, Ethernet, graphics, etc.), the PCI bus supports an industry-... -

Page 98: Vmebus Interface

Functional Description VMEbus Interface The VMEbus interface is implemented with the CA91C042 Universe ASIC. The Universe chip interfaces the 32/64-bit PCI local bus to the VMEbus. The Universe ASIC provides: The PCI-bus-to-VMEbus interface The VMEbus-to-PCI-bus interface The DMA controller functions of the local VMEbus The Universe chip includes Universe Control and Status Registers (UCSRs) for interprocessor communications. -

Page 99: Asynchronous Serial Ports

ISASIO device. For detailed programming information, refer to the PCI and ISA bus discussions in the MVME2603/2604 Programmer’s Reference Guide, listed in Appendix D, Related Documentation, and to the vendor documentation for the ISASIO device. http://www.motorola.com/computer/literature... -

Page 100: Disk Drive Controller

Functional Description Disk Drive Controller The ISASIO device incorporates a PS/2-compatible low- and high-density disk drive controller for use with an optional external disk drive. The drive interfaces with the ISASIO controller via base board connector J4, which relays both power and control signals. The ISASIO disk drive controller is compatible with the DP8473, 765A, and N82077 devices commonly used to implement floppy disk controllers. -

Page 101: Real-Time Clock/Nvram/Timer Function

M48T59/T559 RAM and clock chip to provide 8KB of non-volatile static RAM, a real-time clock, and a watchdog timer function. This chip supplies a clock, oscillator, crystal, power failure detection, memory write protection, 8KB of NVRAM, and a battery in a package consisting of two parts: http://www.motorola.com/computer/literature 3-11... -

Page 102: Programmable Timers

Functional Description A 28-pin 330mil SO device containing the real-time clock, the oscillator, power failure detection circuitry, timer logic, 8KB of static RAM, and gold-plated sockets for a battery ® A SNAPHAT battery housing a crystal along with the battery The SNAPHAT battery package is mounted on top of the M48T59/T559 device. -

Page 103: 16-Bit Timers

Z85230 according to the interrupt source. Interrupt request levels are programmed via the PIB controller. Refer to the Z85230 data sheet and to the MVME2603/ MVME2604 Programmer’s Reference Guide, both listed in Appendix D, Related Documentation, for further information. http://www.motorola.com/computer/literature 3-13... -

Page 104: Z8536 Cio Device

Functional Description Z8536 CIO Device The Z8536 CIO device complements the Z85230 ESCC by supplying modem control lines not provided by the Z85230 ESCC. In addition, the Z8536 CIO device has three independent 16-bit counters/ timers. The Z85230 receives a 5 MHz clock input. Base Module Feature Register The Base Module Feature Register contains the details of the MVME2603/2604 single board computer’s configuration. -

Page 105: P2 Signal Multiplexing

16 time slots are defined and allocated as follows: Table 3-2. P2 Multiplexing Sequence MXDO (From Base Board) MXDI (From MVME761) Time Slot Signal Name Time Slot Signal Name RTS3 CTS3 DTR3 DSR3/MID1 LLB3/MODSEL DCD3 RLB3 TM3/MID0 RTS4 DTR4 CTS4 LLB4 DSR4/MID3 http://www.motorola.com/computer/literature 3-15... -

Page 106: Abort Switch (S1)

Functional Description Table 3-2. P2 Multiplexing Sequence (Continued) MXDO (From Base Board) MXDI (From MVME761) Time Slot Signal Name Time Slot Signal Name RLB4 DCD4 ∗ IDREQ TM4/MID2 DTR1 DTR2 Reserved DSR1 Reserved DCD1 Reserved Reserved DSR2 Reserved DCD2 ABORT Switch (S1) switch is located on the LED mezzanine. -

Page 107: Front Panel Indicators (Ds1 - Ds6)

MVME2603/2604, it does not directly indicate the condition of any single fuse. If the LED flickers or goes out, check all the fuses (polyswitches). (DS6, green). System Controller; lights when the Universe ASIC in the MVME2603/2604 is the VMEbus system controller. http://www.motorola.com/computer/literature 3-17... -

Page 108: Polyswitches (Resettable Fuses)

Functional Description Polyswitches (Resettable Fuses) The MVME2603/2604 base board draws fused +5V DC, +12V DC, and –12V DC power from the VMEbus backplane through connectors P1 and P2. The 3.3V DC and the core processor voltage power is supplied by the on-board +5Vdc. -

Page 109: Speaker Control

RAM200 memory mezzanine. The PowerPC 603 is a 64-bit processor with 32KB on-chip cache (16KB data cache and 16KB instruction cache). The PowerPC 604 is a 64-bit processor with 32KB on-chip cache (16KB data cache and 16KB instruction cache). http://www.motorola.com/computer/literature 3-19... -

Page 110: Flash Memory

Functional Description The Raven bridge controller ASIC provides the bridge between the PowerPC microprocessor bus and the PCI local bus. Electrically, the Raven chip is a 64-bit PCI connection. Four programmable map decoders in each direction provide flexible addressing between the PowerPC microprocessor bus and the PCI local bus. -

Page 111: Mvme712M Transition Module

Green LED for SCSI terminator power; yellow LED for Ethernet transceiver power The features of the P2 adapter board include: A 50-pin connector for SCSI cabling to the MVME712M and/or to other SCSI devices Socket-mounted SCSI terminating resistors for end-of-cable or middle-of-cable configurations http://www.motorola.com/computer/literature 3-21... -

Page 112: Mvme761 Transition Module

Functional Description Fused SCSI terminator power developed from the +5V DC present at connector P2 A 64-pin DIN connector to interface the EIA-232-D, parallel, SCSI, and Ethernet signals to the MVME712M MVME761 Transition Module The MVME761 transition module (Figure 1-12 on page 1-26) and P2 adapter board are used in conjunction with the MVME2603/2604 base board. -

Page 113: Table 3-4. Sim Type Identification

EIA-530 DCE SIM530DTE EIA-530 DTE SIMV35DCE V.35 DCE SIMV35DTE V.35 DTE SIMX21DCE X.21 DCE SIMX21DTE X.21 DTE For additional information about the serial interface modules, refer to the MVME761 User’s Manual (listed in Appendix D, Related Documentation) as necessary. http://www.motorola.com/computer/literature 3-23... -

Page 115: Mvme2603/2604 Connectors

4Connector Pin Assignments MVME2603/2604 Connectors This chapter summarizes the pin assignments for the following groups of interconnect signals for the MVME2603/2604: Connectors with pin assignments common to MVME712M, as well as MVME761-compatible versions of the base board Connector LED Mezzanine Connector J1 on page 4-3 Debug Connector J2 on page 4-4 Floppy/LED Connector J4 on page 4-7 PCI Expansion Connector J5 on page 4-8... - Page 116 Connector Pin Assignments Connectors with pin assignments specific to MVME761- compatible versions of the base board Connector VMEbus Connector P2 on page 4-25 Serial Ports 1 and 2 on page 4-26 Serial Ports 3 and 4 on page 4-27 Parallel Connector on page 4-28 Ethernet 10BaseT/100BaseTX Connector on page 4-29 The following tables furnish pin assignments only.

-

Page 117: Common Connectors

MVME2603/2604. Maximum cable length is 15 feet. The pin assignments are as follows: Table 4-1. LED Mezzanine Connector ∗ RESETSW ∗ No Connection ABORTSW ∗ ∗ PCILED FAILLED ∗ ∗ LANLED STATLED ∗ ∗ FUSELED RUNLED ∗ ∗ SBSYLED SCONLED SPKR http://www.motorola.com/computer/literature... -

Page 118: Debug Connector J2

Connector Pin Assignments Debug Connector J2 A 190-pin connector (J2 on the MVME2603/2604 base board) provides access to the processor bus (MPU bus) and some bridge/memory controller signals. It can be used for debugging purposes. The pin assignments are listed in the following table. Table 4-2. - Page 119 PD33 PD34 PD35 PD36 PD37 PD38 PD39 PD40 PD41 PD42 PD43 PD44 PD45 PD46 PD47 PD48 PD49 PA50 PD51 PD52 PD53 PD54 PD55 PD56 PD57 PD58 PD59 PD60 PD61 PD62 PD63 PDPAR0 PDPAR1 PDPAR2 PDPAR3 PDPAR4 PDPAR5 PDPAR6 PDPAR7 http://www.motorola.com/computer/literature...

- Page 120 Connector Pin Assignments Table 4-2. Debug Connector (Continued) No Connection No Connection ∗ ∗ DBDIS TSIZ0 TSIZ1 TSIZ2 ∗ ∗ CSE0 ∗ GLOBAL CSE1 ∗ ∗ SHARED DBWO ∗ ∗ AACK +3.3V ∗ ∗ ARTY XATS ∗ ∗ DRTY TBST ∗...

-

Page 121: Floppy/Led Connector J4

LED array. The pin assignments are listed in the following table. Table 4-3. Floppy/LED Connector +5VF +5VF LEDDISP0 LEDDISP1 LEDDISP2 LEDDISP3 LEDDISP4 LEDDISP5 LEDDISP6 LEDDISP7 LEDDISP8 LEDDISP9 LEDDISP10 LEDDISP11 LEDDISP12 LEDDISP13 LEDDISP14 LEDDISP15 LEDBLNK F_DENSEL http://www.motorola.com/computer/literature... -

Page 122: Pci Expansion Connector J5

Connector Pin Assignments Table 4-3. Floppy/LED Connector (Continued) F_MSEN0 ∗ F_INDEX ∗ F_MTR0 ∗ F_DR1 ∗ F_DR0 ∗ F_MTR1 ∗ F_DIR ∗ F_STEP ∗ F_WDATA ∗ F_WGATE ∗ F_TRK0 ∗ F_WP ∗ F_RDATA ∗ F_HDSEL ∗ F_DSKCHG PCI Expansion Connector J5 The MVME2603/2604 has provision for stacking a PMC carrier board on the base board for additional PCI expansion. - Page 123 ∗ ∗ STOP FRAME ∗ ACK64 Reserved 64∗ Reserved ∗ PCIRST ∗ ∗ CBE1 CBE0 ∗ ∗ CBE3 CBE2 AD11 AD10 AD13 AD12 AD15 AD14 AD17 AD16 AD19 AD18 AD21 AD20 AD23 AD22 AD25 AD24 AD27 AD26 AD29 AD28 http://www.motorola.com/computer/literature...

- Page 124 Connector Pin Assignments Table 4-4. PCI Expansion Connector (Continued) AD31 AD30 PAR64 Reserved ∗ ∗ CBE5 CBE4 ∗ ∗ CBE7 CBE6 AD33 AD32 AD35 AD34 AD37 AD36 AD39 AD39 AD41 AD40 AD43 AD42 AD45 AD44 AD47 AD46 AD49 AD48 AD51 AD50 AD53 AD52...

-

Page 125: Keyboard And Mouse Connectors J6, J8

(J6) and mouse (J8). The pin assignments for those connectors are listed in the following two tables. Table 4-5. Keyboard Connector K_DATA No Connection +5VF K_CLK No Connection Table 4-6. Mouse Connector M_DATA No Connection +5VF M_CLK No Connection http://www.motorola.com/computer/literature 4-11... -

Page 126: Dram Mezzanine Connector J7

Connector Pin Assignments DRAM Mezzanine Connector J7 A 190-pin connector (J7 on the MVME2603/2604 base board) supplies the interface between the processor bus (MPU bus) and the RAM200 DRAM mezzanine. The pin assignments are listed in the following table. Table 4-7. DRAM Mezzanine Connector ∗... - Page 127 RDL28 RDL29 RDL30 RDL31 RDL32 RDL33 RDL34 RDL35 RDL36 RDL37 RDL38 RDL39 RDL40 RDL41 RDL42 RDL43 RDL44 RDL45 RDL46 RDL47 RDL48 RDL49 RDL50 RDL51 RDL52 RDL53 RDL54 RDL55 RDL56 RDL57 RDL58 RDL59 RDL60 RDL61 RDL62 RDL63 CDL0 CDL1 http://www.motorola.com/computer/literature 4-13...

- Page 128 Connector Pin Assignments Table 4-7. DRAM Mezzanine Connector (Continued) CDL2 CDL3 CDL4 CDL5 CDL6 CDL7 No Connection No Connection RDU0 RDU1 RDU2 RDU3 RDU4 RDU5 RDU6 RDU7 RDU8 RDU9 RDU10 RDU11 RDU12 RDU13 RDU14 +3.3V RDU15 RDU16 RDU17 RDU18 RDU19 RDU20 RDU21 RDU22...

-

Page 129: Pci Mezzanine Card Connectors

PMC2TDO ∗ PMC1P Not Used ∗ PMCINTD Not Used Not Used Not Used Not Used Pull-up +3.3V ∗ PCICLK4 PCIRST Pull-down ∗ PMC1GNT +3.3V Pull-down ∗ PMC1REQ Not Used AD31 AD30 AD29 AD28 AD27 AD26 AD25 AD24 +3.3V http://www.motorola.com/computer/literature 4-15... -

Page 130: Table 4-8. Pci Mezzanine Card Connector (Continued)

Connector Pin Assignments Table 4-8. PCI Mezzanine Card Connector (Continued) ∗ CBE3 IDSEL AD23 AD22 AD21 +3.3V AD20 AD19 AD18 ∗ AD17 AD16 CBE2 ∗ FRAME Not Used ∗ ∗ IRDY TRDY +3.3V ∗ ∗ DEVSEL STOP ∗ ∗ LOCK PERR ∗... - Page 131 Not Used AD35 AD34 Not Used Not Used AD33 Not Used Not Used AD32 Not Used Not Used Not Used Not Used Not Used Not Used Not Used Not Used Not Used Not Used Not Used Not Used http://www.motorola.com/computer/literature 4-17...

-

Page 132: Vmebus Connector P1

Connector Pin Assignments VMEbus Connector P1 Two 160-pin connectors (P1 and P2) supply the interface between the base board and the VMEbus. P1 provides power and VME signals for 24-bit addressing and 16-bit data. Its pin assignments are set by the VMEbus specification. -

Page 133: Mvme712M-Compatible Versions

Table 4-10. VMEbus Connector P2 (MVME712M I/O Mode) Row Z Row A Row B Row C Row D ∗ ∗ SDB8 SDB0 P2C1 PMCIO0 ∗ SDB1 P2C2 PMCIO1 ∗ ∗ ∗ SDB9 SDB2 RETRY P2C3 PMCIO2 ∗ SDB3 VA24 P2C4 PMCIO3 http://www.motorola.com/computer/literature 4-19... - Page 134 Connector Pin Assignments Table 4-10. VMEbus Connector P2 (MVME712M I/O Mode) (Continued) ∗ ∗ SDB10 SDB4 VA25 P2C5 PMCIO4 ∗ SDB5 VA26 P2C6 PMCIO5 ∗ ∗ SDB11 SDB6 VA27 +12VF PMCIO6 ∗ ∗ SDB7 VA28 PR_STB PMCIO7 ∗ SDB12 SDBP0 VA29 PR_DATA0 PMCIO8...

-

Page 135: Scsi Connector

MVME712M transition module. The pin assignments for the SCSI connector are listed in the following table. Table 4-11. SCSI Connector (MVME712M) DB00∗ DB01∗ DB02∗ DB03∗ DB04∗ DB05∗ DB06∗ DB07∗ DBP∗ Reserved TERMPWR ATN∗ BSY∗ ACK∗ RST∗ MSG∗ SEL∗ D/C∗ REQ∗ O/I∗ http://www.motorola.com/computer/literature 4-21... -

Page 136: Serial Ports 1-4

Connector Pin Assignments Serial Ports 1-4 For the MVME2603/2604, the interface for asynchronous ports 1 and 2 and for synchronous/asynchronous ports 3 and 4 is implemented with four EIA-232-D DB25 connectors (J7-J10) located on the front panel of the MVME712M transition module. The pin assignments for serial ports 1-4 on the MVME712M are listed in the following table. -

Page 137: Parallel Connector

MVME712M transition module. The pin assignments are listed in the following table. Table 4-13. Parallel I/O Connector (MVME712M) ∗ PRSTB PRD0 PRD1 PRD2 PRD3 PRD4 PRD5 PRD6 PRD7 ∗ PRACK PRBSY PRPE ∗ PRSEL INPRIME ∗ No Connection PRFAULT http://www.motorola.com/computer/literature 4-23... -

Page 138: Ethernet Aui Connector

Connector Pin Assignments Table 4-13. Parallel I/O Connector (MVME712M) (Continued) No Connection No Connection No Connection No Connection No Connection No Connection No Connection Ethernet AUI Connector The MVME2603/2604 provides both AUI and 10BaseT/100BaseTX LAN connections. For MVME712M-compatible base boards, the LAN interface is an AUI connection implemented with a DB15 connector (J6) located on the MVME712M transition module. -

Page 139: Mvme761-Compatible Versions

SDB13 SBSY VA31 PR_DATA2 PMCIO10 ∗ SACK PR_DATA3 PMCIO11 ∗ ∗ SDB14 SRST PR_DATA4 PMCIO12 ∗ SMSG VD16 PR_DATA5 PMCIO13 ∗ ∗ SDB15 SSEL VD17 PR_DATA6 PMCIO14 ∗ VD18 PR_DATA7 PMCIO15 ∗ ∗ SDBP1 SREQ VD19 PR_ACK PMCIO16 http://www.motorola.com/computer/literature 4-25... -

Page 140: Serial Ports 1 And 2

Connector Pin Assignments Table 4-15. VMEbus Connector P2 (MVME761 I/O Mode) (Continued) ∗ VD20 PR_BUSY PMCIO17 ∗ Not Used VD21 PR_PE PMCIO18 ∗ SLIN VD22 PR_SLCT PMCIO19 ∗ Not Used TxD3 VD23 PR_INIT PMCIO20 ∗ RxD3 PR_ERR PMCIO21 Not Used RTxC3 VD24 TxD1... -

Page 141: Serial Ports 3 And 4

The pin assignments for serial ports 3 and 4 are listed in the following table. Table 4-17. Serial Connections—Ports 3 and 4 (MVME761) No Connection TXDn RXDn RTSn CTSn DSRn DCDn SPn_P9 SPn_P10 SPn_P11 SPn_P12 SPn_P13 SPn_P14 TXCIn SPn_P16 RXCIn http://www.motorola.com/computer/literature 4-27... -

Page 142: Parallel Connector

Connector Pin Assignments Table 4-17. Serial Connections—Ports 3 and 4 (MVME761) LLBn SPn_P19 DTRn RLBn SPn_P23 TXCOn No Connection Parallel Connector Both versions of the base board provide parallel I/O connections. For MVME761-compatible models, the parallel interface is implemented with an IEEE P1284 36-pin connector (J10) located on the MVME761 transition module. -

Page 143: Ethernet 10Baset/100Basetx Connector

Table 4-19. Ethernet 10BaseT/100BaseTX Connector (MVME761) TD– Terminated Terminated RD– Terminated Terminated For detailed descriptions of the various interconnect signals, consult the support information documentation package for the MVME2603/2604 SBC or the support information sections of the transition module documentation as necessary. http://www.motorola.com/computer/literature 4-29... -

Page 145: Chapter 5 Ppcbug

5PPCBug Overview The PowerPC debugger, PPCBug, is a powerful evaluation and debugging tool for systems built around Motorola PowerPC microcomputers. Facilities are available for loading and executing user programs under complete operator control for system evaluation. The PowerPC debugger provides a high degree of functionality and user friendliness, and yet stresses portability and ease of maintenance. -

Page 146: Memory Requirements

(for example, GO), then control may or may not return to PPCBug, depending on the outcome of the user program. The PPCBug is similar to previous Motorola firmware debugging packages (for example, MVME147Bug, MVME167Bug, MVME187Bug), with differences due to microprocessor architectures. -

Page 147: Using The Debugger

At least one space before the first argument. Precede all other arguments with either a space or comma. One or more options. Precede an option or a string of options with a semicolon (;). If no option is entered, the command’s default option conditions are used. http://www.motorola.com/computer/literature... -

Page 148: Debugger Commands

PPCBug Debugger Commands The individual debugger commands are listed in Table 5-1. The commands are described in detail in the PPCBug Firmware Package User’s Manual Note You can list all the available debugger commands by entering the Help (HE) command alone. You can view the syntax for a particular command by entering HE and the command mnemonic, as listed below. - Page 149 I/O Physical (Direct Disk Access) I/O Teach for Configuring Disk Controller Idle MPU Register Display Idle MPU Register Modify Idle MPU Register Set Load S-Records from Host Macro Define/Display NOMA Macro Delete Macro Edit Enable Macro Listing NOMAL Disable Macro Listing Load Macros http://www.motorola.com/computer/literature...

- Page 150 PPCBug Table 5-1. Debugger Commands (Continued) Command Description Save Macros MD, MDS Memory Display MENU System Menu Memory Modify Memory Map Diagnostic Memory Set Memory Write Automatic Network Boot Nap MPU Network Boot Operating System, Halt Network Boot Operating System NIOC Network I/O Control NIOP...

- Page 151 Flash memory is available to you, keep in mind that reprogramming any portion of Flash memory will erase everything currently contained in Caution Flash, including the PPCBug debugger. Note Both banks A and B of Flash contain the PPCBug debugger. http://www.motorola.com/computer/literature...

-

Page 152: Diagnostic Tests

VMEbus to PCI Interface ASIC Tests All boards * VGA543x Video Graphics Tests Not applicable to MVME2600 series boards Z8536 Zilog Z8536 Counter/Timer Tests All boards Notes 1. Some diagnostics depend on restart defaults that are set up only in a particular restart mode. -

Page 153: Overview

6CNFG and ENV Commands Overview You can use the factory-installed debug monitor, PPCBug, to modify certain parameters contained in the PowerPC board’s Non-Volatile RAM (NVRAM), also known as Battery Backed-up RAM (BBRAM). The Board Information Block in NVRAM contains various elements concerning operating parameters of the hardware. -

Page 154: Cnfg - Configure Board Information Block

= "07 " System Serial Number = "1463725 " System Identifier = "Motorola MVME2600" License Identifier = "12345678 " The parameters that are quoted are left-justified character (ASCII) strings padded with space characters, and the quotes (") are displayed to indicate the size of the string. -

Page 155: Env - Set Environment

System is the standard mode of operation, and is the default mode if NVRAM should fail. System mode is defined in the PPCBug Firmware Package User’s Manual. Field Service Menu Enable [Y/N] = N? Display the field service menu. Do not display the field service menu. (Default) http://www.motorola.com/computer/literature... - Page 156 CNFG and ENV Commands Remote Start Method Switch [G/M/B/N] = B? The Remote Start Method Switch is used when the MVME2600/MVME3600/MVME4600 is cross-loaded from another VME-based CPU, to start execution of the cross-loaded program. Use the Global Control and Status Register to pass and start execution of the cross-loaded program.

- Page 157 Local SCSI bus is not reset on debugger setup. (Default) Local SCSI Bus Negotiations Type [A/S/N] = A? Asynchronous SCSI bus negotiation. (Default) Synchronous SCSI bus negotiation. None. Local SCSI Data Bus Width [W/N] = N? Wide SCSI (16-bit bus). Narrow SCSI (8-bit bus). (Default) http://www.motorola.com/computer/literature...

- Page 158 CNFG and ENV Commands NVRAM Bootlist (GEV.fw-boot-path) Boot Enable [Y/N] = N? Give boot priority to devices defined in the fw-boot- path global environment variable (GEV). Do not give boot priority to devices listed in the fw- boot-path GEV. (Default) Note When enabled, the GEV (Global Environment Variable) boot takes priority over all other boots, including Autoboot and...

- Page 159 (1, 2, 3, 4) until it finds the first “bootable” partition. That is then the partition that will be booted. Other acceptable values are 1, 2, 3, or 4. In these four cases, the partition specified will be booted without searching. http://www.motorola.com/computer/literature...

- Page 160 CNFG and ENV Commands Auto Boot Abort Delay = 7? The time in seconds that the Autoboot sequence will delay before starting the boot. The purpose for the delay is to allow you the option of stopping the boot by use of the <Break> key. The time value is from 0-255 seconds.

- Page 161 The address where the network interface configuration parameters are to be saved/retained in NVRAM; these parameters are the necessary parameters to perform an unattended network boot. A typical offset might be $1000, but this value is application-specific. (Default = $00001000) http://www.motorola.com/computer/literature...

- Page 162 CNFG and ENV Commands If you use the NIOT debugger command, these parameters need to be saved somewhere in the offset range $00001000 through $000016F7. The NIOT parameters do not exceed 128 bytes in size. The setting of this ENV Caution pointer determines their location.

- Page 163 PPCBug. DRAM Parity Enable [On-Detection/Always/Never - O/A/N] = O? DRAM parity is enabled upon detection. (Default) DRAM parity is always enabled. DRAM parity is never enabled. Note This parameter (above) also applies to enabling ECC for DRAM. http://www.motorola.com/computer/literature 6-11...

-

Page 164: Configuring The Vmebus Interface

CNFG and ENV Commands L2 Cache Parity Enable [On-Detection/Always/Never - O/A/N] = O? L2 Cache parity is enabled upon detection. (Default) L2 Cache parity is always enabled. L2 Cache parity is never enabled. PCI Interrupts Route Control Registers (PIRQ0/1/2/3) = 0A0B0E0F? Initializes the PIRQx (PCI Interrupts) route control registers in the IBC (PCI/ISA bus bridge controller). - Page 165 PCI Slave Image 2 Bound Address Register = 22000000? The configured value is written into the LSI2_BD register of the Universe chip. PCI Slave Image 2 Translation Offset = D0000000? The configured value is written into the LSI2_TO register of the Universe chip. http://www.motorola.com/computer/literature 6-13...

- Page 166 CNFG and ENV Commands PCI Slave Image 3 Control = C0400000? The configured value is written into the LSI3_CTL register of the Universe chip. PCI Slave Image 3 Base Address Register = 2FFF0000? The configured value is written into the LSI3_BS register of the Universe chip.

- Page 167 VMEbus Slave Image 3 Base Address Register = 00000000? The configured value is written into the VSI3_BS register of the Universe chip. VMEbus Slave Image 3 Bound Address Register = 00000000? The configured value is written into the VSI3_BD register of the Universe chip. http://www.motorola.com/computer/literature 6-15...

- Page 168 CNFG and ENV Commands VMEbus Slave Image 3 Translation Offset = 00000000? The configured value is written into the VSI3_TO register of the Universe chip. PCI Miscellaneous Register = 10000000? The configured value is written into the LMISC register of the Universe chip.

-

Page 169: Appendix A Specifications

ASpecifications Specifications Table A-1 lists the general specifications for MVME2603/2604 base boards. Subsequent sections detail cooling requirements and FCC compliance. A complete functional description of the MVME2603/2604 base boards appears in Chapter 3, Functional Description. Specifications for the optional PCI mezzanines can be found in the documentation for those modules. -

Page 170: Cooling Requirements

(base board and modules) at a velocity typically achievable by using a 100 CFM axial fan. Temperature qualification is performed in a standard Motorola VME system chassis. 25-watt load boards are inserted in two card slots, one on each side, adjacent to the board under test, to simulate a high power density system configuration. -

Page 171: Fcc Compliance

Front panel screws properly tightened. For minimum RF emissions, it is essential that the conditions above be implemented. Failure to do so could compromise the FCC compliance of the equipment containing the module. http://www.motorola.com/computer/literature... -

Page 173: Introduction

The MVME2603/2604 hardware supports asynchronous serial baud rates of 110B/s to 38.4KB/s. For detailed programming information, refer to the PCI and ISA bus discussions in the MVME2600 Series Single Board Computer Programmer’s Reference Guide, listed in Appendix D, Related Documentation, and to the vendor documentation for the ISASIO device. -

Page 174: Eia-232-D Connections

Serial Interconnections synchronous (SDLC/HDLC) and asynchronous protocols. The hardware supports asynchronous serial baud rates of 110B/s to 38.4KB/s and synchronous baud rates of up to 2.5MB/s. Each port supports the CTS, DCD, RTS, and DTR control signals, as well as the TxD and RxD transmit/receive data signals and TxC/RxC synchronous clock signals. -

Page 175: Table B-1. Eia-232-D Interconnect Signals

Receive Clock. Output from terminal to modem; clocks input data from the terminal to the modem. 18, 19 Not used. Data Terminal Ready. Input to modem from terminal; indicates that the terminal is ready to send or receive data. Not used. http://www.motorola.com/computer/literature... - Page 176 Serial Interconnections Table B-1. EIA-232-D Interconnect Signals (Continued) Signal Signal Name and Description Number Mnemonic Ring Indicator. Output from modem to terminal; indicates that an incoming call is present. The terminal causes the modem to answer the phone by carrying DTR true while RI is active. Not used.

-

Page 177: Interface Characteristics

2500pF. Table B-3. EIA-232-D Interface Receiver Characteristics Value Parameter Unit Minimum Maximum ±25 Input signal voltage 2.25 Input high threshold voltage Input low threshold voltage 0.75 Input hysteresis Ω Input impedance (−15V < V < +15V) 3000 7000 http://www.motorola.com/computer/literature... -

Page 178: Eia-530 Connections

Serial Interconnections EIA-530 Connections The EIA-530 interface complements the EIA-232-D interface in function. The EIA-530 standard defines the mechanical aspects of this interface, which is used for transmission of serial binary data, both synchronous and asynchronous. It is adaptable to balanced (double-ended) as well as unbalanced (single-ended) signaling and offers the possibility of higher data rates than EIA-232-D with the same DB-25 connector. -

Page 179: Table B-4. Mvme761 Eia-530 Interconnect Signals

TxCO_A Transmit Signal Element Timing—DTE (A). Control signal that clocks output data. TM_A Test Mode (A). Indicates whether the local DCE is under test. In DTE configuration, ignored. In DCE configuration, always tied inactive and driven false. http://www.motorola.com/computer/literature... -

Page 180: Interface Characteristics

Serial Interconnections Interface Characteristics In specifying parameters for serial binary data interchange between DTE and DCE devices, the EIA-530 standard assumes the use of balanced lines, except for the Remote Loopback, Local Loopback, and Test Mode lines, which are single-ended. Balanced-line data interchange is generally employed in preference to unbalanced-line data interchange where any of the following conditions prevail: The interconnection cable is too long for effective unbalanced... -

Page 181: Proper Grounding

The terminals should not have a connection between the logic ground return and the chassis. http://www.motorola.com/computer/literature... -

Page 183: Table C-1. Troubleshooting Mvme2603/2604 Boards

CTroubleshooting CPU Boards: Solving Startup Problems Introduction In the event of difficulty with your CPU board, try the simple troubleshooting steps on the following pages before calling for help or sending the board back for repair. Some of the procedures will return the board to the factory debugger environment. - Page 184 Troubleshooting CPU Boards: Solving Startup Problems Table C-1. Troubleshooting MVME2603/2604 Boards (Continued) Condition Possible Problem Try This: II. There is a A. The keyboard or Recheck the keyboard and/or mouse connections and power. display on the mouse may be terminal, but connected input from the incorrectly.

- Page 185 Or, it may indicate a test that failed. If neither happens, enter: de <CR> Any errors logged should now be displayed. If there are any errors, go to step VI. If there are no errors, go to step V. http://www.motorola.com/computer/literature...

- Page 186 Troubleshooting CPU Boards: Solving Startup Problems Table C-1. Troubleshooting MVME2603/2604 Boards (Continued) Condition Possible Problem Try This: V. The debugger A. No apparent No further troubleshooting steps are required. is in system problems — mode and the troubleshooting board is done. autoboots, or the board has passed self-...

-

Page 187: Motorola Computer Group Documents

DRelated Documentation Motorola Computer Group Documents The Motorola publications listed below are referenced in this manual. You can obtain paper or electronic copies of Motorola Computer Group publications by: Contacting your local Motorola sales office Visiting MCG’s World Wide Web literature site, http://www.motorola.com/computer/literature... -

Page 188: Manufacturers' Documents

Number PowerPC 603 RISC Microprocessor Technical Summary MPC603E/D MPC604E/D PowerPC 604 RISC Microprocessor Technical Summary Literature Distribution Center for Motorola Telephone: 1-800- 441-2447 FAX: (602) 994-6430 or (303) 675-2150 Web Site: http://e-www.motorola.com/webapp/DesignCenter/ E-mail: ldcformotorola@hibbertco.com PowerPC 603 RISC Microprocessor User’s Manual... - Page 189 Document Title and Source Number ® PowerPC Microprocessor Family: The Programming Environments for MPCFPE/AD 32-Bit Microprocessors Literature Distribution Center for Motorola Telephone: 1-800- 441-2447 FAX: (602) 994-6430 or (303) 675-2150 Web Site: http://e-www.motorola.com/webapp/DesignCenter/ E-mail: ldcformotorola@hibbertco.com IBM Microelectronics Programming Environment Manual...

- Page 190 Related Documentation Publication Document Title and Source Number SCC (Serial Communications Controller) User’s Manual SCC/ESCC User’s (for Z85230 and other Zilog parts) Manual Web Site: http://www.zilog.com/pdfs/serial/scc_escc_iscc_manual/contents.html Z8536 CIO Counter/Timer and Parallel I/O Unit DM10001176 Product Specification and User’s Manual ® (in Z8000 Family of Products Data Book) Web Site: http://www.zilog.com/products/zx80dev.html#um...

-

Page 191: Related Specifications

Web Site: http://standards.ieee.org/catalog/ IEEE - PCI Mezzanine Card Specification (PMC) P1386.1 Draft 2.0 Institute of Electrical and Electronics Engineers, Inc. Web Site: http://standards.ieee.org/catalog/ Bidirectional Parallel Port Interface Specification IEEE Standard 1284 Institute of Electrical and Electronics Engineers, Inc. Web Site: http://standards.ieee.org/catalog/ http://www.motorola.com/computer/literature... - Page 192 Web Site: http://www.ibm.com PowerPC Microprocessor Common Hardware Reference Platform: A ISBN System Architecture (CHRP), Version 1.0 1-55860-394-8 Literature Distribution Center for Motorola Telephone: 1-800- 441-2447 FAX: (602) 994-6430 or (303) 675-2150 Web Site: http://e-www.motorola.com/webapp/DesignCenter/ E-mail: ldcformotorola@hibbertco.com Morgan Kaufmann Publishers, Inc.

- Page 193 (This document can also be obtained through the national standards body of member countries.) Interface Between Data Terminal Equipment and Data Circuit- TIA/EIA-232 Terminating Equipment Employing Serial Binary Data Interchange; Standard Electronic Industries Alliance; Web Site: http://global.ihs.com/index.cfm (for publications) http://www.motorola.com/computer/literature...

- Page 195 Index conductive chassis rails configuration Abort (interrupt) signal 3-16 base board abort (interrupt) signal MVME712M transition module 1-14 adapter board, P2 1-14, 1-25, 1-45, 1-49, 3-5, configuration, base board serial port 1-8, 3-21 1-10, 1-11, 1-12 adapter, P2 configuration, I/O 1-3, 1-14, 1-25 for MVME761 1-33...

- Page 196 Index disk drive controller 3-10, ground connections DMA channels 2-13 documentation, related hardware features DRAM headers, setting 1-6, 1-13 base address 1-50 DRAM speed 6-10 I/O handling 1-3, 1-14, 1-25 IBC DMA channel assignments 2-13 EIA-232-D installation interconnections MVME712M transition module 1-44 EIA-530 MVME761 transition module...

- Page 197 6-10 operating parameters ROMNAL 6-11 P2 adapter SCSI for MVME761 1-33 cabling 1-45 MVME712M 1-24 interface MVME761 1-32 termination P2 adapter board 1-14, 1-25, 1-45, 1-49, 3-5, terminator power 1-52, 3-18, 3-19 3-21 SCSI bus P2 multiplexing 1-48 http://www.motorola.com/computer/literature IN-3...

- Page 198 Index serial communications interface 3-13, serial interface VME64 bus extension serial interface modules (SIMs) 3-22 VMEbus serial interface parameters address/data configurations 1-50 serial port configuration, base board 1-8, Universe ASIC and 1-10, 1-11, 1-12 VMEbus interface 6-12 serial port configuration, transition module 1-17, 1-27 serial ports 3-8,...