Motorola MVME2600 Series Manuals

Manuals and User Guides for Motorola MVME2600 Series. We have 4 Motorola MVME2600 Series manuals available for free PDF download: Reference Manual, Installation And Use Manual, Programmer's Reference Manual

Motorola MVME2600 Series Reference Manual (283 pages)

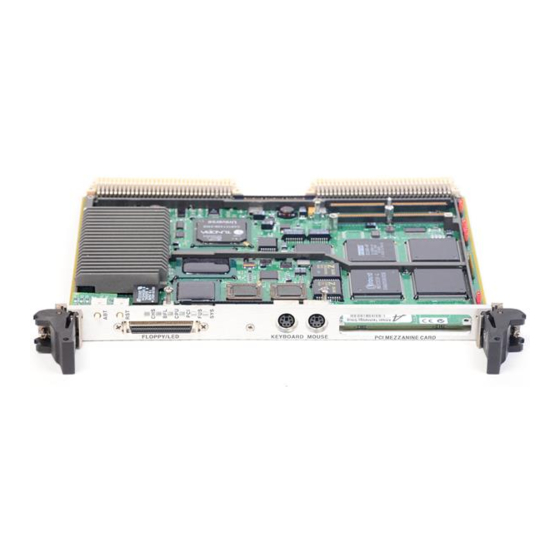

MVME2600/2700 Series Single Board Computer

Brand: Motorola

|

Category: Motherboard

|

Size: 0.86 MB

Table of Contents

Advertisement

Motorola MVME2600 Series Installation And Use Manual (198 pages)

Single Board Computer

Brand: Motorola

|

Category: Motherboard

|

Size: 1.54 MB

Table of Contents

Motorola MVME2600 Series Installation And Use Manual (20 pages)

Brand: Motorola

|

Category: Single board computers

|

Size: 0.12 MB

Advertisement

Motorola MVME2600 Series Programmer's Reference Manual (20 pages)

Brand: Motorola

|

Category: Single board computers

|

Size: 0.12 MB