Advertisement

Quick Links

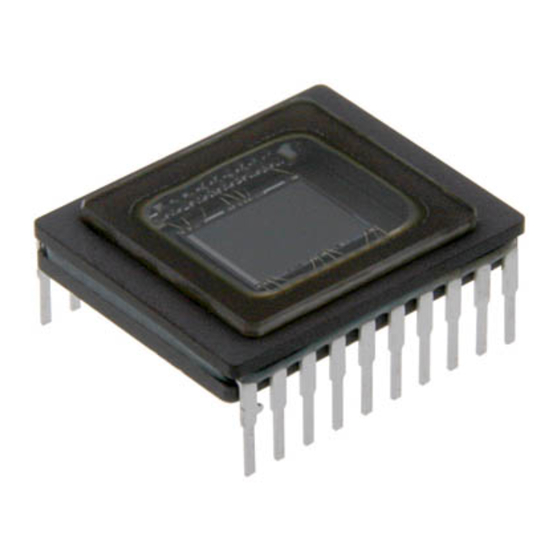

Diagonal 8mm (Type 1/2) CCD Image Sensor for NTSC Color Video Cameras

Description

The ICX418AKL is an interline CCD solid-state

image sensor suitable for NTSC color video cameras

with a diagonal 8mm (Type 1/2) system. Compared

with the current product ICX038DNA, basic

characteristics such as sensitivity, smear, dynamic

range and S/N are improved drastically.

This chip features a field period readout system and

an electronic shutter with variable charge-storage

time. This chip is compatible with the pins of the

ICX038DNA and has the same drive conditions.

Features

• High sensitivity (+6.0dB compared with the ICX038DNA)

• Low smear (–5.0dB compared with the ICX038DNA)

• High D range (+2.0dB compared with the ICX038DNA)

• High S/N

• High resolution and low dark current

• Excellent antiblooming characteristics

• Ye, Cy, Mg, and G complementary color mosaic filters on chip

• Continuous variable-speed shutter

• Substrate bias:

Adjustment free (external adjustment also possible with 6 to 14V)

• Reset gate pulse: 5Vp-p adjustment free (drive also possible with 0 to 9V)

• Horizontal register: 5V drive

Device Structure

• Interline CCD image sensor

• Optical size:

• Number of effective pixels: 768 (H)

• Total number of pixels:

• Chip size:

• Unit cell size:

• Optical black:

• Number of dummy bits:

• Substrate material:

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Diagonal 8mm (Type 1/2)

494 (V) approx. 380K pixels

811 (H)

508 (V) approx. 410K pixels

7.40mm (H)

5.95mm (V)

8.4µm (H)

9.8µm (V)

Horizontal (H) direction: Front 3 pixels, rear 40 pixels

Vertical (V) direction:

Horizontal 22

Vertical 1 (even fields only)

Silicon

– 1 –

ICX418AKL

20 pin DIP (Cer-DIP)

V

3

Pin 11

Optical black position

Front 12 pixels, rear 2 pixels

Pin 1

2

12

H

40

(Top View)

E01503B41

Advertisement

Summary of Contents for Sony ICX418AKL

- Page 1 Silicon Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices.

- Page 2 Notice which will be available to you in the latest specifications book for the Products. You should abide by the latest version of this Notice. If a Sony subsidiary or distributor has its own use restriction notice on the Products, such a use restriction notice will additionally apply between you and the subsidiary or distributor.

- Page 3 Output circuit supply voltage Signal output Horizontal Register Pin No. – 3 – Note) Note) : Photo sensor Symbol Description Substrate bias circuit supply voltage DSUB Reset drain bias Reset gate clock Horizontal register transfer clock Horizontal register transfer clock ICX418AKL...

- Page 4 –0.3 to +50 –0.3 to +18 –55 to +10 –15 to +20 to +10 to +15 to +17 –17 to +17 –10 to +15 –55 to +10 –65 to +0.3 –0.3 to +30 –30 to +80 °C –10 to +60 °C ICX418AKL...

- Page 5 = 9.0V Symbol Min. Typ. – 5 – Typ. Max. Unit Remarks 15.0 15.45 15.0 15.45 15.45 15.0 Typ. Max. Unit Remarks 15.0 15.45 15.0 15.45 14.0 10.5 11.0 11.5 12.0 12.5 13.0 Max. Unit Remarks 10.0 ICX418AKL 13.5 14.0...

- Page 6 Vp-p Min. Typ. Max. Unit –0.2 Vp-p – 6 – Waveform Remarks diagram = (V = (V n – V High-level coupling High-level coupling Low-level coupling Low-level coupling Low-level coupling Waveform Remarks diagram ICX418AKL n (n = 1 to 4)

- Page 7 Capacitance between reset gate clock and GND Capacitance between substrate clock and GND Vertical transfer clock series resistor Vertical transfer clock ground resistor Vertical transfer clock equivalent circuit Symbol Horizontal transfer clock equivalent circuit – 7 – Min. Typ. Max. Unit 2700 2700 ICX418AKL Remarks...

- Page 8 Drive Clock Waveform Conditions (1) Readout clock waveform 100% (2) Vertical transfer clock waveform = (V = (V n – V n (n = 1 to 4) – 8 – ICX418AKL...

- Page 9 Negative overshoot level during the falling edge of RG is V (5) Substrate clock waveform 100% Point A is the minimum value of the coupling waveform during the period from RGLL RGLm – 9 – ICX418AKL + 0.5V is the average value of V RGLH...

- Page 10 Typ. Max. Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. 5.38 5.38 Min. Typ. Max. – 10 – Unit µs During readout 0.01 0.01 µs 0.01 0.01 When draining µs charge Unit Remarks and H is two. ICX418AKL Remarks...

- Page 11 Y signal output (3dB down 6.3MHz) LPF2 (3dB down 1MHz) – 11 – (Ta = 25°C) Measurement Remarks method Ta = 60°C Zone 0 and I Zone 0 to II' Ta = 60°C Ta = 60°C [ C] Chroma signal output ICX418AKL...

- Page 12 B in the B field) As a result, the sequence of charges output as signals from the horizontal shift register (Hreg) is, for line A1, (G + Cy), (Mg + Ye), (G + Cy), and (Mg + Ye). Hreg – 12 – ICX418AKL...

- Page 13 , color temperature of 3200K halogen source) as a subject. (Pattern [dB] (1/10V method conversion value) 100 [%] 100 [%] 100 [%] – 13 – ICX418AKL...

- Page 14 Adjust the Y signal output value generated by strobe light to 200mV. After setting the strobe light so that it strobes with the following timing, measure the residual signal (Ylag). Substitute the value into the following formula. Lag = (Ylag/200) 100 [%] Strobe light timing Output Light Y signal output 200mV Ylag (lag) – 14 – ICX418AKL...

- Page 15 Drive Circuit 1 (substrate bias internal generation mode) XSUB CXD1267AN XSG1 XSG2 22/20V 100k 1/35V 22/16V 20 19 18 17 16 15 14 13 12 11 0.01 0.01 3.3/20V 9 10 ICX418 (BOTTOM VIEW) 0.01 [ A] CCD OUT 3.9k –9V 3.3/16V...

- Page 16 Drive Circuit 2 (substrate bias external adjustment mode) XSUB CXD1267AN XSG1 XSG2 22/20V 1/35V 1/35V 100k 1/35V 22/16V 20 19 18 17 16 15 14 13 12 11 0.01 270k 0.01 3.3/20V 9 10 ICX418 (BOTTOM VIEW) 0.01 [ A] CCD OUT 3.9k –9V...

- Page 17 Spectral Sensitivity Characteristics (Excludes lens characteristics and light source characteristics) Sensor Readout Clock Timing Chart Odd Field Even Field Wave Length [nm] 2.5 2.5 2.5 33.5 – 17 – ICX418AKL Unit: µs...

- Page 18 Drive Timing Chart (Vertical Sync) 2 4 6 1 3 5 2 4 6 1 3 5...

- Page 19 Drive Timing Chart (Horizontal Sync)

- Page 20 If a load is applied to the entire surface by a hard component, bending stress may be generated and the package may fracture, etc., depending on the flatness of the ceramic portions. Therefore, for installation, use either an elastic load, such as a spring plate, or an adhesive. Shearing strength Tensile strength – 20 – ICX418AKL 0.9Nm Torsional strength...

- Page 21 For continuous using under cruel condition exceeding the normal using condition, consult our company. b) Exposure to high temperature or humidity will affect the characteristics. Accordingly avoid storage or usage in such conditions. – 21 – ICX418AKL...

- Page 22 Package Outline Unit: mm PACKAGE STRUCTURE PACKAGE MATERIAL Cer-DIP LEAD TREATMENT TIN PLATING LEAD MATERIAL 42 ALLOY PACKAGE MASS 2.6g DRAWING NUMBER AS-B14-01(E) 20pin DIP (600mil) 18.0 ± 0.4 14.6 1. “A” is the center of the effective image area. 2.